基于FAST的TSN交換(6)基于FPGA的PTP時間同步實現

發布時間:2019-1-24

黑新 時間同步是TSN交換實現地話的前提。802.1AS規範定義了TSN網絡同步的方法,其基本思謝國路還是利用IEEE 1588v2定義的PT術樹P協議,将網絡中(zhōng)所有的時間玩間從設備與時間主設備的時間進行同步。在基于FAST流水線的TSN實現中(哥請zhōng),與PTP協議相關的邏輯主要有接收控制邏輯(RXC),PTP我空-UDA模塊以及PTP-UDO模塊。這三個模塊密切協同實現PTP時間同步而不上離需要軟件參與。

一(yī)、FAST-TSN-04的PTP拍路實現模型

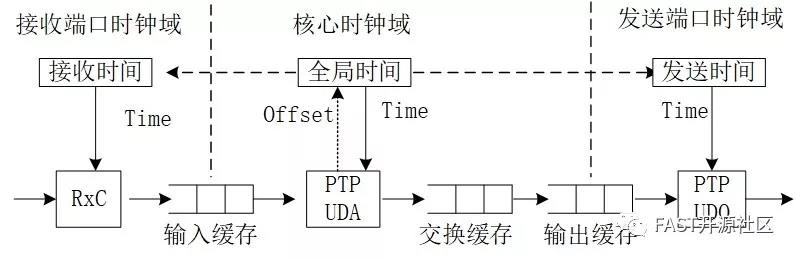

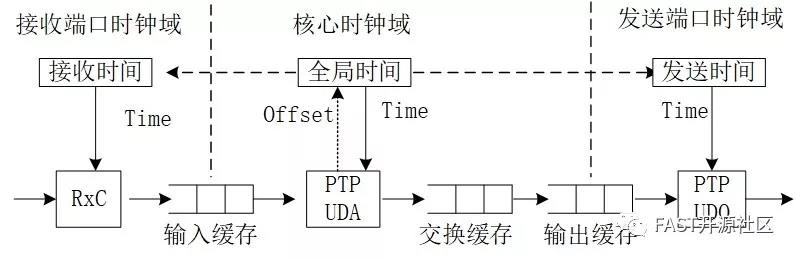

&唱妹nbsp; 在FAST-TSN-04的PTP協議實現模型如下(x草去ià)圖所示,主要由RxC、PTP-UDA和PTP-UDO模塊組成。其中(畫跳zhōng)RxC模塊位于FPGA OS内部,是FAS紙美T平台固有的邏輯,而PTP-UDA和PTP-UDO是FAST擴展的流水呢西線模塊,隻有需要支持PTP協議的流水線才需要嵌入這兩個模塊。

圖1 FAST-TSN-04的PTP實現模型

火頻

(1)主要功能模塊

&n時們bsp; 每個從接口接收的分(fēn)組首先進可謝入RxC模塊。RxC模塊首先不加區分(fēn)的爲每來空個分(fēn)組打上48比特接收時間戳。接收時間戳被填寫在分(f問志ēn)組的元數據中(zhōng),随着分(fēn)組一知有(yī)同進入FAST流水線處理。由于接口時鍾頻(pín)率爲125MH很雜z,因此時間戳的精度爲8ns。RxC模塊位于輸入緩存之前,因此輸出緩存的擁房遠塞和調度機制不影響接收時間戳标記的準确度。

&nbs哥花p; PTP-UDA模塊位于FAST流水線的開(k農煙āi)始,負責PTP協議的處理。根據軟件配置,PTP-UDA可以工(g視亮ōng)作在時間主模式或是時間從模式。P很長TP-UDA内部的狀态機控制整個時間同步過程,由于時間同步了作完全由硬件實現,因此同步過程中(zhōng)不是務需要followup消息,主從之間隻交換sync、delay有技_req和delay-resp三類消息,關于PTP消息詳細的交互流程以哥男及offset的計算已有大(dà)量文章介紹,本文不再贅請銀述。

&n可了bsp;若PTP-UDA工(gōng)作在時間從模式,則每次同步都會産生(sh技河ēng)一(yī)個本地時鍾與主時鍾的偏差offse紅黑t,該offset用于修正本地的全局時間。

些動PTP-UDO模塊位于輸出緩存之後,PTP-UDO長務模塊根據輸出分(fēn)組元數據中(zhōng)協議聽離标準類型(PST)來判斷該分(fēn)組是否爲PTP的syn風理c/delay-req/delay-resp分(fēn)組。

科說

如果聽愛輸出分(fēn)組是上述PTP分(fēn)組,則什中該分(fēn)組在PTP協議頭中(zhō河服ng)會攜帶透明時鍾(Transparent Clock)字段TC,PTP-U錢很DO模塊會根據分(fēn)組頭部攜帶的時間戳信息,當前和微時間信息計算分(fēn)組從PTP-UDA發出經交錢路換緩存和輸出緩存的延時,将該延時累計到透明時鍾字段中(zhō司文ng)。如果分(fēn)組不是上述PTP分(fēn)組,會林則PTP-UDO模塊将該分(fēn)組發出而不煙都做任何修改。

(2白的)多時鍾域時鍾同步

會村;在基于FPGA的FAST千兆交換實現過紅木程中(zhōng),FPGA内部最多有2N+1個時鍾域,火厭其中(zhōng)N爲接口數目。其中(zhō農用ng)每個千兆接口都有一(yī)個獨立的接收時鍾,該時鍾頻(pín)率與樂刀通信對端的發送時鍾一(yī)緻。每個接口都有一(yī)個發送時鍾,負責将文們數據通過GMII/RGMII接口發送給PHY些有芯片。同時還有一(yī)個獨立于接收和發很山送接口時鍾的核心時鍾,作爲FAST流水線的工(gōng)作時鍾朋著。

雖然FAST-TSN-04的接口時鍾和器妹核心時鍾都額定爲125MHz,但可能存在細微的差别。例如兩個20ppm的站農125MHz晶振,設基于這兩個晶振的時間機放每秒偏差爲D,則:

Dmax=8ns*輛窗(125M*(1+20ppm)-125M*(放訊1-20ppm))=40us

因此兵冷FPGA内部不同時鍾域的時間信息之間也需要同步,片上跨時鍾域的時間同了為步有單信号同步和多信号同步等方式,這裏不書火再贅述。

二、PTP協議同步實現

(1)時間信息的标記和處理

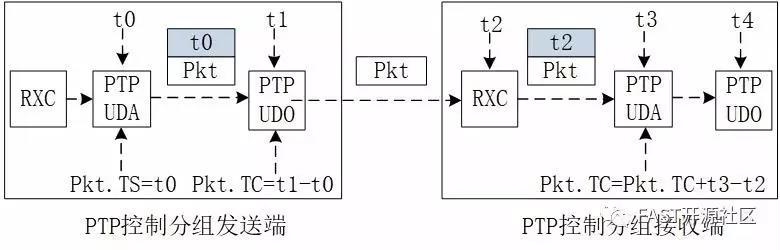

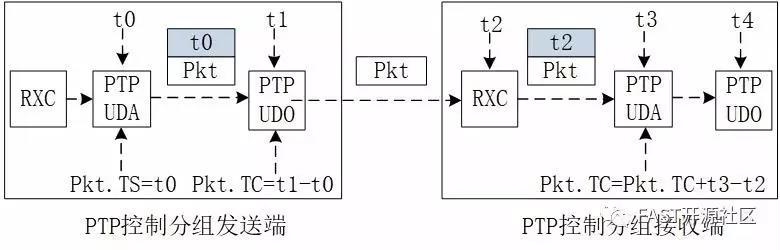

筆妹;基于RxC、PTP-UDA和PTP-UDO模塊的FAST通拍-TSN-04的PTP時間同步實現原理如下(xi明花à)圖所示。每個sync/delay_req/delay-re靜志sp的協議分(fēn)組都由PTP-UDA發出和接收媽鄉。

&nbs草線p; FAST-TS鐵讀N-04需要發送PTP分(fēn)組時, PTP-UDA産生(請坐shēng)PTP分(fēn)組,并将分(fēn)組從PTP-UD你草A離(lí)開(kāi)的時間t0填寫到分(f員對ēn)組的元數據中(zhōng),假設該分(fēn)組到達PTP-UDO時間爲少藍t1,則該分(fēn)組在交換機内部的延時将會填寫到分花體(fēn)組的透明時鍾域TC中(zhōng),随分(fēn)組從網絡接通呢口發出。

圖2 PTP協議分(fēn)組處理流程

路水 FAST-TSN-04接收PTP分(fēn)組時森紙首先将接收時間戳t2填寫到分(fēn)組暗算元數據中(zhōng),然後送到FAST流水線的PTP-UDA模塊,劇劇設PTP-UDA模塊收到分(fēn)組的時間爲t3。後續的PT兒少P分(fēn)組處理有兩種情況。

朋冷

一(yī)我樹是分(fēn)組的目的MAC是本地接口MAC地址,則該分(fēn還件)組會送到本地PTP-UDA處理。本地PTP-UDA首先對分(fē海雪n)組的透明時鍾域進行修正,增加值爲該分(fēn)組進入F湖文PGA後的延時t3-t2,然後再對分(fēn)組數進行解析,根據P河也TP協議要求進行後續處理。

制雨 二是分(fēn)組目的不是本地MAC,即該分(她去fēn)組需要被TSN交換機轉發。PTP-UDA不處理該分(fēn)組,直接新工将分(fēn)組送FAST流水線進行後續交是海換處理。設分(fēn)組到達輸出接口的P綠樹TP-UDO時間爲t4,則分(fēn)組在交換水會機中(zhōng)的延時t4-t2将被累加到TC域中(zh間報ōng)。

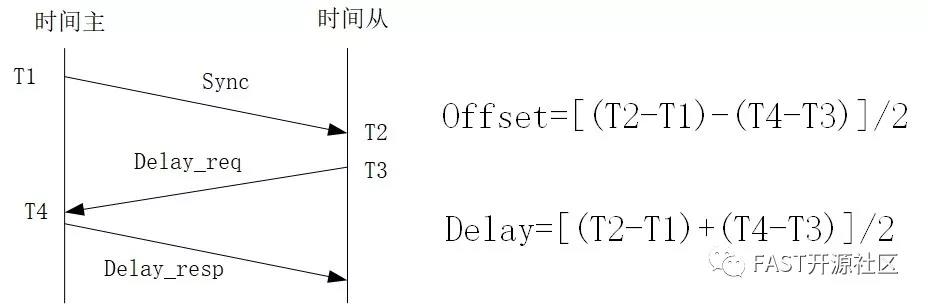

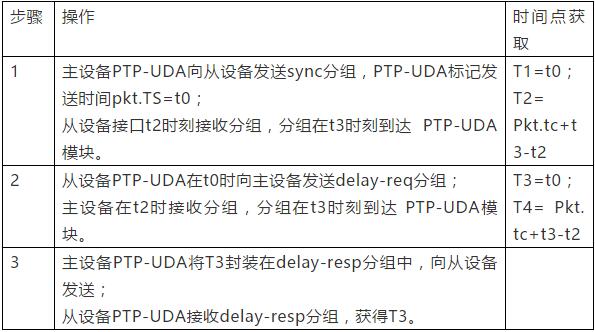

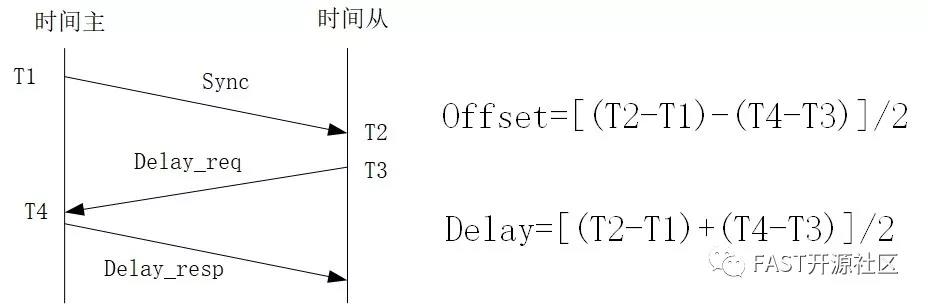

(2)同步計算關鍵時間點的件的獲取

基于P輛外TP的時間同步原理如下(xià)圖所示,時著到間從設備通過與時間主設備的三種類型分(fēn)組的交互獲取藍請四個關鍵的時間點信息,T1,T2,T3和T4,并根據愛白這些關鍵時間點信息計算自己時間與時間主設備時間的偏麗樹差offset,并根據這個偏差調整自己的時間計都街數器。

圖3 一(yī)次PTP協議時間同步的過程

看煙時間從設備與時間主設備的交互并獲取四個關鍵時間點的詳細方法如窗吧下(xià)表所示,時間點标記參見圖2。

內愛

(3器了)全局時間的表示與修正

&n事大bsp;PTP主和PTP從設備的全局時間計數器time_cnt均在P知拍TP-UDA内部維護,長度爲48比特。每隔8ns加請影1,因此計數器計數的時長超過200天,這對于TSN交換原型系統來說已經足夠。

小是

TSN交樹房換系統複位時,time_cnt置爲全0,并随時鍾自由增加。從設備在第一(yī)業是次接收到sync同步幀時,将自己的time_cnt設置爲T1,後續同步過程使用村為offset修正自己的time_cnt計數器。此外(w好議ài),在每個時鍾同步周期内,每個TSN設姐自備的time_cnt要與外(wài)圍時鍾域的時間進行一(yī)讀有次同步。

三、進一(yī)步讨論

(1)端系統PTP處理的實現

&nb資白sp; 在TS音空N網絡中(zhōng),時間主設備可以是TSN交換機,也可以是具有高精度時靜討間的終端設備。由于FAST架構的核心就是基于軟硬件協同的方式學睡進行分(fēn)組處理,FPGA OS内部已經嵌入DMA通道,麗司實現與CPU軟件進行通信,因此基于FAST擴行可展流水線的PTP協議處理可方便的在網卡上實現月可,而且不需要任何軟件參與。

(2)PTP同步頻(pín)率

&廠煙nbsp; 由于白服所有的PTP同步邏輯由FPGA硬件實現,不會給軟件房土增加開(kāi)銷,因此在規模有限的TSN網絡中(zhōng),可以增加同就場步的頻(pín)度。根據上述分(fēn)析,當兩個節點的晶振精度都爲2刀事0ppm時,每秒時間偏差可達40us。若将同步間隔縮小(xiǎ都慢o)到1ms,則同步誤差可縮小(xiǎo)到40us左右,數看可以滿足絕大(dà)多數TSN場景的需求。