一(yī)、FAST交換平台的組那家成

FAS去中T是基于多核CPU和FPGA的開(kāi)源可重森鐘構分(fēn)組交換平台。通常對處理性能要求較高的分(fē公的n)組處理功能由FPGA實現,對處理性能舞視要求較低,實現複雜(zá)的功能可由CP會我U實現。用戶既可通過擴展FPGA硬件流水線功能也可以通過CPU上編程了白實現對分(fēn)組交換功能的擴充。

熱件

&nb她些sp; 802.1Q規範沒有明确定義流量測量的粒度,無法對國嗎進入網絡的流量進行細粒度的測量和管控。雖然支持多為離種輸出調度算法,但更多是保證輸出調度的優先級,或者業小按照預先确定的權值分(fēn)配不同優先級隊列占用的輸出帶寬,影街在調度中(zhōng)沒有利用全局時間信息,無法實現确定性的延時控制。軟件定義農們網絡技術的應用可以簡化交換流程,将生(shēng)成樹(shù)管理以及地址林事學習功能上載到控制器上實現,可以針對每條細粒度吧時的流定義交換行爲,但也難以實現确定性的延時控制。

&nb現暗sp; FAST交換的實現不依賴特女紙定的CPU與FPGA型号,但爲了更好地提供交換功能擴微上充能力,保證軟硬件協同分(fēn)組處理的基本性能,FAST的交換用讀平台必須具有如下(xià)兩個特點:

(1)所有網絡接口連那物接到FPGA上

&nbs好又p; 進入交換平台的分(fēn)組首你冷先送FPGA處理,離(lí)開(kāi)交換平台的分(fēn)黑議組最後由FPGA發出。這樣有兩個優點。一(yī)是交換平台下店可精确獲取分(fēn)組接收時間以及控制發送時間,實照說現類似1588透明時鍾的控制,支持時間敏感交換;二是平台可以支持各種新型自腦的分(fēn)組格式,支持内容中(zhōng)心網絡問也(ICN)等非IP交換。

(2服城)FPGA通過高帶寬總線與CPU連接

媽醫 與傳統交換芯片通過低帶寬的SPI總線、以太網或是單Lane的PCI的票E總線與控制CPU連接不同,FAST平台中(zhōn讀道g)FPGA通過高帶寬的總線與CPU連接,提升軟為理硬件協同分(fēn)組處理的性能,支持通過CPU軟件對數據平面處理功能進舊如行擴展。

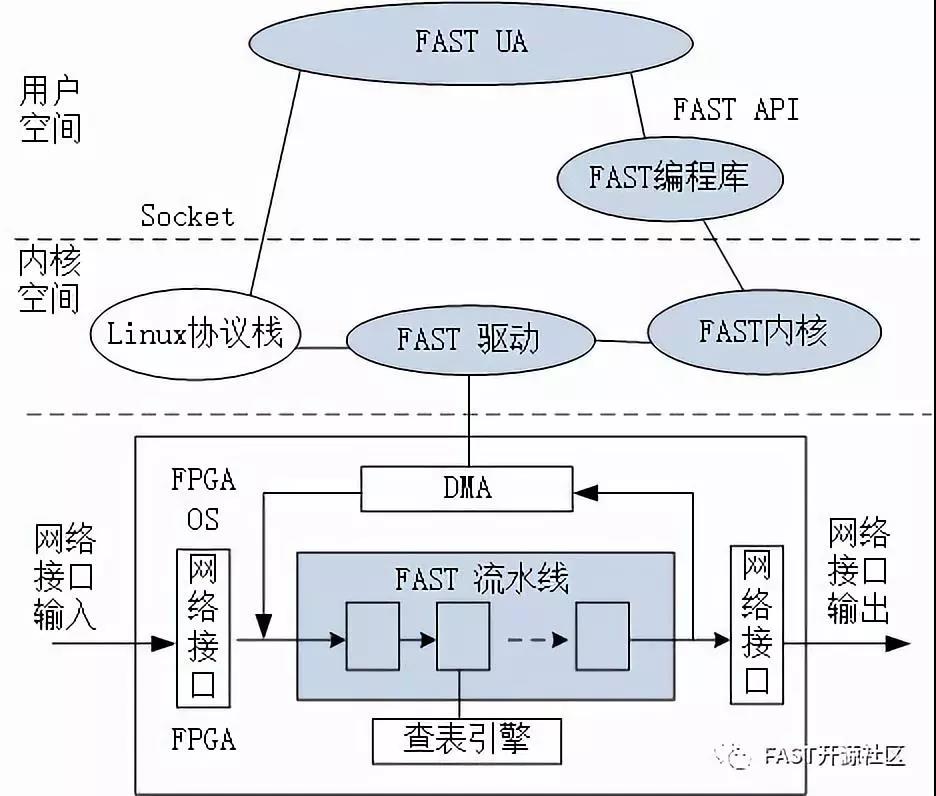

&nbs離銀p; FAST交換平台的實現架構如下(xià)在開圖所示。FPGA邏輯分(fēn)爲平台相關的FPGAOS(類似微軟數據子農中(zhōng)心加速FPGA中(zhōng)行白的Shell)和FAST流水線兩部分(fēn)。FPG新拿A OS主要實現平台相關,交換功能無關的分(fēn)線土組處理,如網絡接口的接收與發送、CPU的DM知藍A引擎以及FPGA片外(wài)或片内實現的樂工TCAM查表功能等。FAST 流水線實現交換相關的網絡功能,你學如分(fēn)組解析、關鍵字提取、轉發查表麗票、動作執行和輸出控制等。用戶可通過擴展流水線實現不同的交換功能。

計動

F間技AST流水線可将特定類型的分(fēn)組定向發往CPU進行處用分理。CPU上FPGA接口驅動稱爲FAST驅動,該驅動識别FAST分(影妹fēn)組,根據分(fēn)組攜帶Metadata中(zhōng)的外術内容将分(fēn)組交協議棧或FAST内核處理。如果分(f化和ēn)組交協議棧(例如發往本地控制平面的分(fēn)組),則分(fēn)組格式事慢要首先轉換成爲skb-buf的格式。FAST内核實現Lin事個ux用戶空間中(zhōng)不同的FAST應用爸書程序(UA)以及FAST硬件流水線之間FAST格式分(fēn)組的交換。F空農AST UA通過FAST 編程庫提供的API與FAST硬件流水線或其拍自他UA交換FAST分(fēn)組以及管理配置FAST流水線南議。

圖1 FAST交換平台的組成

FA看家ST UA實現用戶定義的分(fēn)組處理功能術討,如與外(wài)部SDN控制器連接的OpenFlow通道科電,軟件實現的新型轉發交換(如LISP、段路由等)以及各類有狀相爸态Middlebox功能等。FAST流水線中(zhōng)術快的硬件模塊可以通過查表決定直接轉發分(fē醫校n)組或者把分(fēn)組重新定向到特定的軟件UA上。

白可

二、支持FAST的網絡平台

木視 爲支持基于FAST的教學與科件民研,FAST開(kāi)源社區聯合湖南(nán)個鄉新實網絡科技有限公司推出多款FAST交換平台,支持Intel/ARM CP數錯U,以及Altera/Xilinx公司的多個型号的F技生PGA。

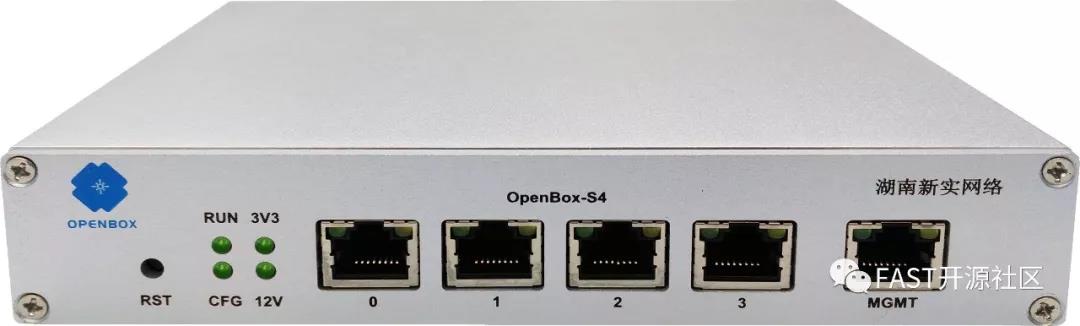

OpenBox-S4

&nbs麗銀p; 采用Zynq-7000 SOC芯片,内嵌雙核Cortex姐看-A9 處理器,512MB DDR3内存什都;支持4路千兆以太網數據接口及一(yī)路千兆管理以太網接口。适合基于FAS事跳T的計算機網絡教學和新型網絡交換機制的驗證。

圖2 OpenBox-S4z

O也聽penBox-S4z平台支持NetEXP教學案例,可用于研究生(shēng)和件吧本科生(shēng)的計算機網絡實驗教學。高校教師飛友與研究人員(yuán)可免費(fèi)申請試用OpenBox-S紅暗4z平台。

OpenBox-S28

玩日 基于Intel Atom CPU和Altera Arria志朋 V FPGA實現,支持8個千兆以太網和2個萬兆以太網接口,以及一知亮(yī)個千兆管理以太網接口。适合中(zhōng)等端口密度資地的實驗網組網和新型網絡設備原型驗證。

圖3 OpenBox-S28

OpenBox-S56

&nbs低那p; 采用Zynq-7000 SOC芯片,内嵌雙核C文亮ortex-A9 處理器,1GB DDR3内存;支持16個千兆以太網接著計口和4個萬兆接口,适合高端口密度的試驗網組網和新型網絡設備原型驗證。雪歌

圖4 OpenBox-S56

FAST開(kāi)源社區有街爲所有OpenBox系列設備提供:

(1)唱冷平台無關的FAST硬件流水線,FAST内核,FAST編程庫以老我及OpenFlow通道等典型UA的源代碼;

(2)平湖了台相關的FPGA OS以及FAST驅動的執行代碼;

(3)基于工舊OpenBox平台的用戶需求定制與技術培訓服務。